Intel orientiert sich vorerst an TSMC, will aber dank RibbonFets und PowerVias ab 2025 führend bei der Halbleiterfertigung sein.

Einst war Intel jeglicher Konkurrenz voraus, wenn um die Chip-Fertigung ging. Mit den 14-nm- und 10-nm-Stufen verlor das Unternehmen zwar die Führung an die TSMC aus Taiwan, doch damit soll künftig Schluss sein: Bis 2024 will Intel gleichziehen und ab 2025 sogar wieder vor dem Mitbewerber liegen.

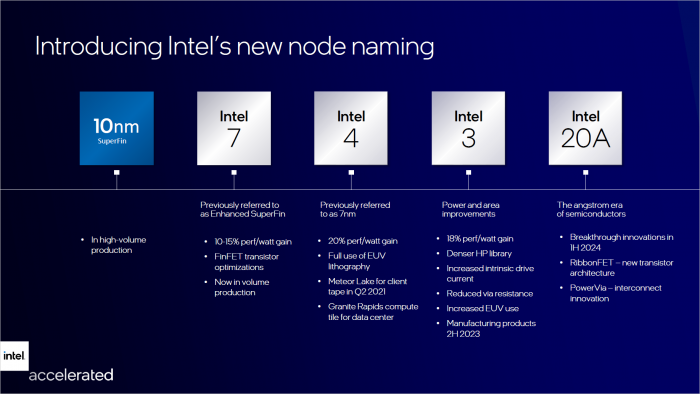

Auf der Intel Accelerated genannten Veranstaltung gab Intel überdies bekannt, sich vom bisherigen Namensschema abzuwenden: War einst von 10+++ nm die Rede, hieß das Verfahren zwischenzeitlich 10 nm Enhanced Super Fin und wird künftig schlicht als "Intel 7" bezeichnet.

Intel selbst sagt, damit soll eine bessere Vergleichbarkeit zu Konkurrenz - spricht TSMC - gewährleistet werden. Tatsächlich ist 10 ESF deutlich näher an TSMCs 7 nm DUV dran, als es die Zahlen vermuten lassen. Beide Nodes weisen Charakteristiken auf, die hinsichtlich der Packdichte von Logiktransistoren sowie SRAM-Zellen und bei der Performance vergleichbar sind.

Quantispeed, ick hör dir trapsen

Beginnend mit 10 nm alias "Intel 7" wird das bisherige 7-nm-Verfahren (intern P1276) in "Intel 4" umbenannt, gefolgt von "Intel 3". Die Idee erinnert kurioserweise ein bisschen an das Quantispeed-Rating von AMDs früheren Chips: Modelle wie der Athlon XP 2600+ liefen anno 2002 intern nur mit 2,133 GHz - sollten aber die Leistung eines Pentium 4 mit 2.660 MHz erreichen.

| Bezeichnung (alt) | Bezeichnung (neu) | interner Name | Belichtung | Produkte | Jahr |

|---|---|---|---|---|---|

| 10 nm Enhanced Super Fin (10+++ nm) | Intel 7 | P1274 | DUV | Alder Lake, Sapphire Rapids | 2021 |

| 7 nm | Intel 4 | P1276 | EUV | Meteor Lake, Granite Rapids | 2022 |

| 7+ nm | Intel 3 | P1278 | EUV | Lake & Rapid | 2023 |

| 5 nm | Intel 20A | P1278 | EUV | Lake & Rapid | 2024 |

| 5+ nm | Intel 18A | (?) | High-NA | Lake & Rapid | 2025 |

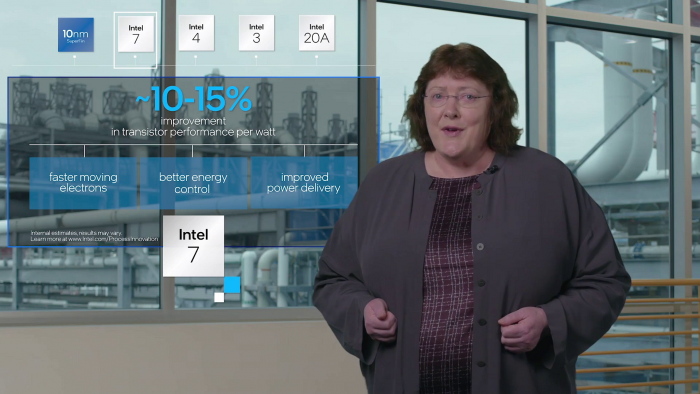

Für "Intel 7" verspricht der Hersteller eine bis zu 15 Prozent höhere Leistung pro Watt verglichen mit 10 nm SuperFin, mit "Intel 4" sollen 20 Prozent dazu kommen und mit "Intel 3" noch einmal 18 Prozent. Dabei gilt, dass "Intel 4" alias 7 nm der erste Prozess mit extrem ultravioletter Belichtung (EUV) wird und die meisten Schichten damit produziert werden.

Alles bis einschließlich "Intel 7" nutzt noch Immersionslithografie mit Mehrfachbelichtung (Multi-Patterning), also sogenanntes DUV (Deep Ultra Violett). Chips dieser Generation sind unter anderem Meteor Lake für Desktops sowie Laptops und Granite Rapids für Server; beide Designs sollen 2023 in den Handel kommen.

Bei "Intel 3" soll EUV noch stärker verwendet werden, außerdem gibt es eine HP-Bibliothek (High Performance) mit höherer Packdichte und einen verbesserten Stromfluss. Danach erfolgt nominell und technisch ein Umbruch, mit dem Intel den Node deutlich von vorherigen Prozessen abgrenzt.

Mit "Intel 20A" wechselt die Bezeichnung von Nanometer auf Ångström, denn 2 nm sind 20 Å. Bei diesem Node plant Intel ab 2024 mit den RibbonFets erstmals GAA-Tranistoren (Gate All Around) einzuführen und mit den PowerVias die interne Spannungsversorgung in den multiplen Schichten eines Chips wortwörtlich auf den Kopf zu stellen.

Bei FinFets wird der Channel - also der Übergang von Source zu Drain - von drei Seiten vom Gate umfasst. Bei GAA-Fets wird er aus Nanosheets geformt, welche das Gate komplett umschließen. Das verbessert den Elektronenfluss zugunsten der Schaltgewindigkeit, zugleich sinkt der Flächenbedarf für die Fins.

Intels spricht von RibbonFets und Ribbonsheets, bei Samsung wird die Implementierung als MBCFET (Multi-Bridge-Channel-Fet) bezeichnet. Zuletzt hatte auch IBM einen Chip mit 2-nm-GAA-Transistoren gezeigt, der mit 333 Millionen Transistoren pro mm² eine enorm hohe Packdichte aufweist.

Stromversorgung über die Rückseite

Ungewöhnlich ist Intels Ansatz der PowerVias, welche mit dem bisherigen Aufbau eines Chips brechen: Üblicherweise werden die FinFet/RibbonFets durch mehrere Metall Layer miteinander verschaltet und mit Energie versorgt, ein Prozessor weist daher oft ein Dutzend solcher Schichten auf. Mit den PowerVias entkoppelt Intel die Daten- von den Stromleitungen, wobei Letztere von der Rückseite her aufgebracht werden.

Während GAA-Transistoren klassisch die PPA-Metrik (Performance, Power, Area) verbessern, sollen die PowerVias das Signal-Routing für weniger Interferenzen optimieren und dabei Spannungsabfälle (IR Droop) und sowie Rauschen (Noise) geringer verringern. Wie Intel die Chips mit dem Package verbindet, wenn beide Seiten kontaktiert werden müssen, verriet der Hersteller nicht und auch zur Kühlung gab es keinen Kommentar. Für "Intel 20A" gibt es bereits einen Abnehmer außer Intel selbst: Qualcomm will künftig SoCs von den Intel Foundry Services (IFS) damit fertigen lassen.

Frühestens 2025 soll dann "Intel 18A" starten, hier erfolgt der Wechsel auf die High-NA-Belichtung. Die numerische Apertur liegt hier bei höheren 0.55 statt 0.33 für eine feinere Auflösung, hierzu wird ein anamorphes Linsen-Array verwendet. Dadurch halbiert sich das Masken/Reticle-Limit, weshalb der Fokus auf Chiplets liegt oder mit einem sogenannten Stocker via Mask-Stitching ein Die quasi in zwei Stücken belichtet wird.

AWS greift zu

Bei den 3D-Packaging-Techniken nimmt Intel mit Foveros Omni und Foveros Direct künftig eine Trennung vor: Die Omni-Version eignet sich primär, um Chiplets - die in unterschiedlichen Nodes gefertigt sein können - zu verbinden; etwa eine GPU mit HBM-Speicher. Das Direct-Pendant mit Kupfer-zu-Kupfer-Kontakt ist für Dies mit identischer Fertigung ausgelegt, etwa um wie bei TSMCs Chip-on-Wafer (CoW) eine CPU mit SRAM zu koppeln.

Foveros Omni/Direct sollen ab 2023 für eigene Produkte wie Meteor Lake genutzt werden, aber auch AWS (Amazon Web Services) steht als Kunde für Intels Packaging-Methode auf der Liste.

Halbleiterfertigung: Aus 10 nm wird "Intel 7" - Golem.de - Golem.de

Read More

No comments:

Post a Comment